# REPTAR Development Board

# **Reference Manual**

# **Table of Content**

| 1. INTRODUCTION                    | 4  |

|------------------------------------|----|

| 2. GENERAL DESCRIPTION             | 5  |

| 2.1 BLOCK DIAGRAM                  |    |

| 2.2 BOARD COMPONENTS BLOCKS        |    |

| 3. BOARD COMPONENTS AND INTERFACES | 10 |

| 3.1 BOARD OVERVIEW                 | 10 |

| 3.1.1 FPGA board overview          |    |

| 3.1.2 CPU board overview           |    |

| 3.2 COMPONENTS AND FUNCTIONALITIES |    |

| 3.3 DETAILS DRAWINGS               |    |

| 3.4 USB INTERFACE                  |    |

| 3.5 CLOCKING CIRCUITRY             | 21 |

| 3.6 JTAG CHAINS                    |    |

| 3.6.1 FPGA                         |    |

| 3.6.2 CPU                          |    |

| 4. DIMENSIONS                      | 23 |

| 5. POWER SUPPLIES                  | 25 |

| 6. ADDITIONAL INFORMATION          |    |

| 6.1 REVISION HISTORY               | 26 |

| 62 CONTACT                         |    |

# **Table of figures**

| T. A. DEDTELD                                  | _  |

|------------------------------------------------|----|

| FIGURE 1 - REPTAR BLOC DIAGRAM                 | 5  |

| FIGURE 2 - FPGA BOARD DETAILS                  | 11 |

| FIGURE 3 - CPU BOARD DETAILS                   | 12 |

| FIGURE 4- FPGA GENERAL USER INTERFACES         | 18 |

| FIGURE 5 – FPGA CONFIG & DEBUG SWITCHES        | 18 |

| FIGURE 6 - FPGA JUMPERS                        | 19 |

| FIGURE 7 - CPU LABEL REFERENCES                | 19 |

| FIGURE 8 - USB SUB-SYSTEM                      | 20 |

| FIGURE 9 – SPARTAN6 CLOCKS SUB-SYSTEM          | 21 |

| FIGURE 10 - JTAG CHAIN                         | 22 |

| FIGURE 11 - FPGA BOARD DIMENSIONS              | 23 |

| FIGURE 12 - CPU BOARD DIMENSIONS               | 23 |

| FIGURE 13 - REPTAR BOARD SIDE VIEW             | 24 |

| Table List                                     |    |

| Table 1 - Components & Functionalities details | 17 |

| T. D. F. A. Dryveyov Hygmony                   | 20 |

#### 1. INTRODUCTION

REPTAR is a modular extensible platform for teaching and R&D in the HES-SO and beyond...

#### TEACHING

REPTAR is a Universal board for workshops, courses in computer architecture and embedded processor-based systems. The REPTAR platform allows federating various laboratories by providing a common platform.

REPTAR combines an OMAP processor type based on DaVinci DM3730 from Texas Instrument (which itself consists of a core-A8 ARM and a DSP) with a programmable component (FPGA) Xilinx Spartan 6. The platform also includes a large number of control devices, display and communication. Modular in design, it offers many possibilities for expansion.

From a programming perspective, the workshops can be done in different ways:

- Development at the application level or in the processor core with OS or RTOS without intervention in FPGA.

- Development without low-level OS and without intervention in FPGA

- Application Development in the FPGA without CPU usage

- Mix development of processor and FPGA code

#### RESEARCH AND DEVELOPPMENT

REPTAR is a development platform suitable for many research projects, making it unnecessary, at least initially, the realization of a project dedicated board.

#### 2. GENERAL DESCRIPTION

REPTAR is a board that offers a unique opportunity to customize your development environment via many expansion connectors, I/O and daughter cards.

The REPTAR board is made of two boards:

The CPU and the FPGA board

The FPGA board is considered as the mainboard of the REPTAR system. All the power supplies are located on this board. The CPU board is then considered as a daughter card for the system itself. Nevertheless, it is possible to use it separately by connecting it to an optional power supply board<sup>1</sup>.

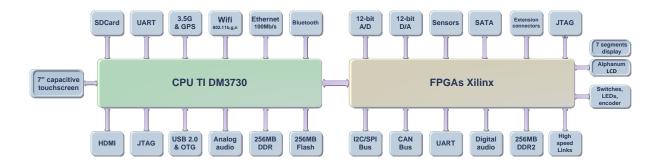

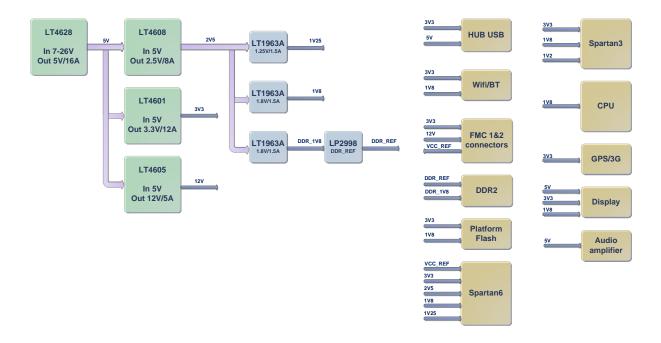

#### 2.1 BLOCK DIAGRAM

The figure below depicts a functional block diagram of the REPTAR board.

Figure 1 - REPTAR bloc diagram

This illustration shows the complexity of the REPTAR system. Not less than 28 peripherals are present on it. These peripherals will be described in the next chapters.

janvier 2013 - 5 - REDS

<sup>&</sup>lt;sup>1</sup> Available on demand

### 2.2 BOARD COMPONENTS BLOCKS

- Processor module DM3730 based on Cortex-A8 (compatible with OMAP 3)

- 1 GHz operating frequency

- 256MB of DDR memory

- 256MB of flash memory

- SD-card interface

- Display interface for TFT / HDMI output

- UART / I2C / SPI interfaces

- 100Mbit Ethernet interface

- 16 bit linear audio stereo DAC / ADC

- MIC and Line In & Out

- USB 2.0 Host and OTG interfaces

- Capacitive touch screen interface

#### FPGA Xilinx Spartan6

- XC6SLX150TFGG900-3

- 147'443 Logic elements

- 184'304 Flip-flop

- 1'335Kbit of distributed RAM

- 4'824Kbit of Blocks RAM

- 4 MCB

- 8 Transceivers (GTP) @ 3GHz

### Configuration subsystem

- Xilinx Spartan3 AN XC3S200AN-5FTG256C

- · Bitstream stored in internal flash

- Used for Spartan6 download

- Xilinx PlatformFlash XCF32P

- Store up to 4 compressed bitstream for Spartan6

### Display interfaces

- EDT 7" display with capacitive touch screen

- 800 x 480

- · I2C for touch

- LCD display

- 4 x 20 lines

- 7-segments

### Memory subsystem

- External DDR2 SDRAM device (on Spartan6 FPGA)

- · 256MB

- · @ 800 MHz

- Parallel Flash memory (on CPU module)

- 256MB

- DDR SDRAM device (on CPU module)

- 256MB

- · @ 400 MHz

- SD-card interface (on CPU module)

#### Clock management system

- One 150MHz (for SATA subsystem)

- One 125MHz (for PCle subsystem)

- One 100MHz for Spartan6 internal logic

- One 100MHz for Spartan3AN internal logic

- One slow clock at 25MHz for both Spartan6 and Spartan3AN internal logic

- The Spartan6 FPGA distributes the following clocks from its internal PLLs:

- External DDR2 memory

- PCle interface

- SATA interface

#### Wired and Wireless communication subsystem

- 100Mbit Ethernet feature (on CPU module)

- WIFI & Bluetooth Module

- IEEE 802.11 b/g/n compatible

- BT 2.1 compatible

- GPS & GSM Module

- PCI Express mini card full size module

- · HSPA, UMTS, EDGE, GPRS and SMS capabilities

- Assisted-GPS

#### Expansion connectors

- Two FMC LPC connectors

- Provides each 34 differential lines or 58 single-ended signals

- It also provides one serial high speed differential pair, clocks, a JTAG Interface and an I2C interface

- One DHB DDK connector

- · Provides 78 GPIOs signals from Spartan6 FPGA

### heig-vol Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud

# **REPTAR**Reference manual

#### General User Interface

All these components are located either on the CPU or on the FPGA board and provide an easier way to debug the user designs.

- Leds and buttons

- Switches

- Headers

#### Serial interfaces

All these interfaces are connecting the CPU, FPGA and various sensors together.

- 120

- SPI

- CAN

#### Audio subsystem

- 16 bit audio stereo analog

- · One mini jack line In

- · One mini jack line Out (pre-amp)

- · One mini jack Microphone

- Digital audio

- One Toslink receiver

- One Toslink transmitter

#### USB subsystem

- 6 Host connectors

- 1 OTG connector

- 1 USB-UART connection direct to FPGA

- 1 USB-UART connection direct to CPU for debugging

#### High speed links

- Three SMB connectors provide access to the high speed transceivers of the Spartan6

- One differential input

- · One differential output

- One reference input clock

- A PCI Express connection between Spartan6 and CPU board<sup>2</sup>

- · Provides 2 lanes

- Internal or external reference clock

- A SATA 1 link between Spartan6 and CPU board <sup>2,3</sup>

- An external SATA 1 connector from Spartan6<sup>3</sup>

<sup>&</sup>lt;sup>2</sup> Not available on CPU board revision 1.0

<sup>&</sup>lt;sup>3</sup> Require a third party vendor IP – not provided by the REDS

### Sensors and actuators

- Temperature sensor

- Light sensor

- Buzzer

- Incremental encoder

### AD & DA converters

- 12-bit ADC

- · Quad channels

- SPI interface

- · Single 3V-to-5V power supply

- 12-bit DAC

- · Quad channels

- 1 MHz sample rate

- · SPI interface

- Analog Supply Range: 2.7 to 5.25V

- Digital Supply Range: 1.7 to 5.25 V

#### 3. BOARD COMPONENTS AND INTERFACES

### 3.1 BOARD OVERVIEW

Chapter 3 provides operational and connectivity details for the major components and interfaces of the board and is divided into the following blocks:

- Main devices

- DM3730 CPU module

- Spartan 6

- Spartan 3AN

- Display

- TFT 7" with capacitive touch screen

- Memory

- DDR/DDR2

- Flash

- SD-card

- Communications

- USB interface

- High-speed serial interface

- Expansion connectors

- General user interfaces

- Jumpers

- Connectors

- Buttons

- Sensors and Actuators

- AD & DA

- Audio

- Analogic

- Digital

- Clocking circuitry

- Configuration circuitry

- Debugging

- Connectors

- JTAG

- UART

- Power supply

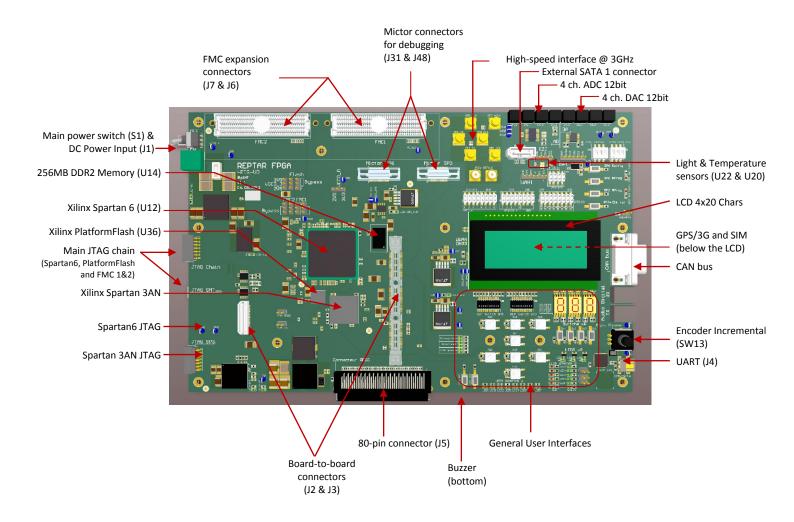

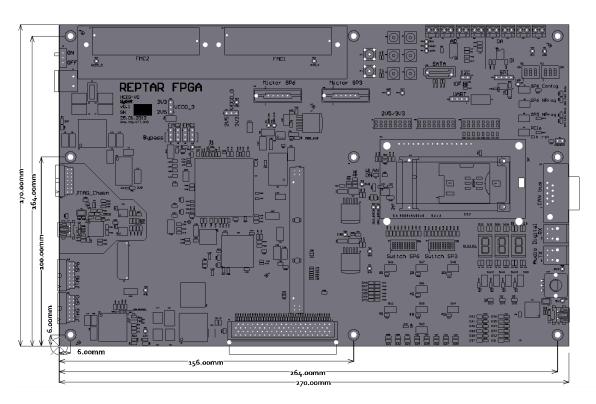

#### 3.1.1 FPGA board overview

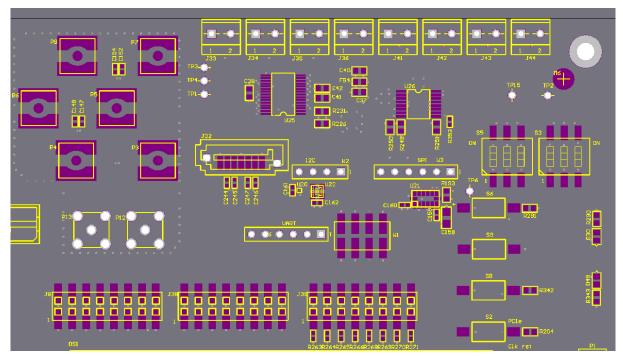

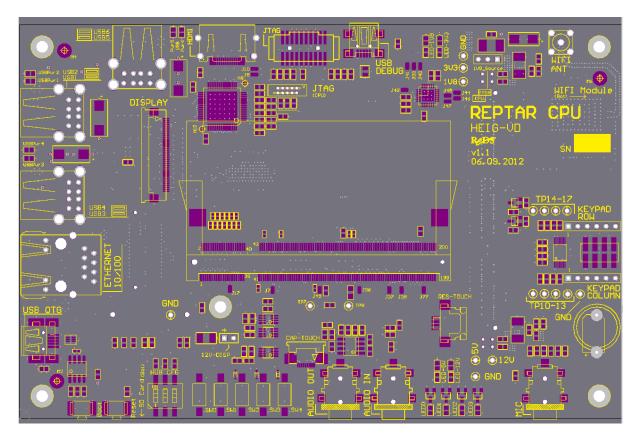

The picture below depicts where are located all the different functionalities described in the following chapters.

Figure 2 - FPGA Board details

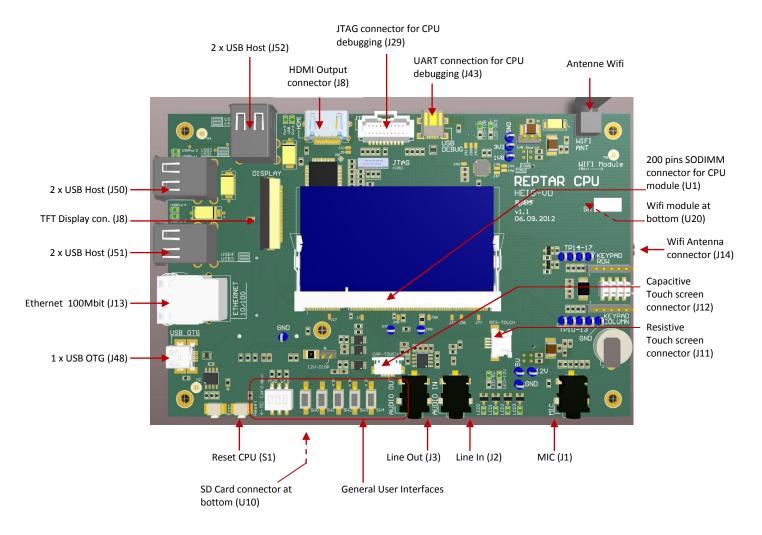

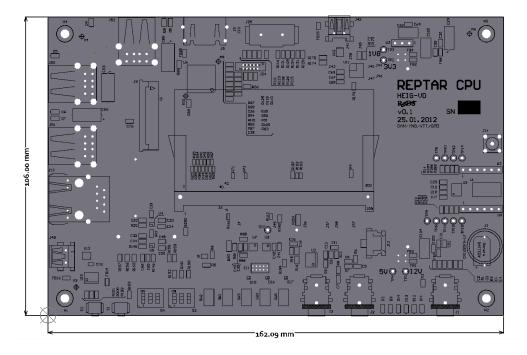

#### 3.1.2 CPU board overview

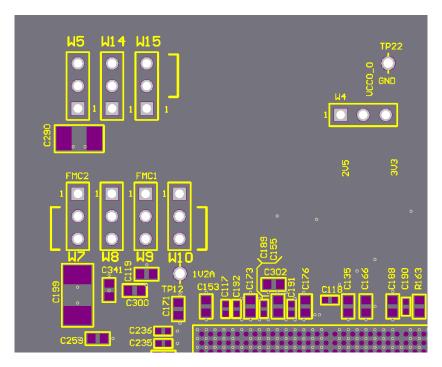

The picture below depicts where are located all the different functionalities described in the following chapters.

Figure 3 - CPU Board details

# **3.2** COMPONENTS AND FUNCTIONALITIES

This table describes the main components and their functionalities.

| Туре          | Components / Interfaces                                   | Board<br>Reference  | Description                                                                                                                                                                                                                                                      | Board<br>Location |

|---------------|-----------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Main devices  | meriaces                                                  | Nererence           |                                                                                                                                                                                                                                                                  | Location          |

| FPGA          | Xilinx Spartan6<br>XC6SLX150TFGG9<br>00-3                 | U12                 | Provides computation power and access to peripherals of the board. Linked to the CPU local bus                                                                                                                                                                   | FPGA<br>(fig.2)   |

| FPGA          | Xilinx Spartan 3AN<br>XC3S200AN-<br>5FTG256C              | U29                 | Used to configure the Spartan6 from either the CPU or the on-board PlatformFlash. Linked to the CPU local bus                                                                                                                                                    | FPGA<br>(fig.2)   |

| Processor     | Module Variscite<br>VAR-SOM-OM37                          | U1                  | Package 200 pins SODIMM.  Based on a TI DM3730 (Cortex A8). Linked to all the FPGAs through its local bus.                                                                                                                                                       | CPU<br>(fig.3)    |

| Display       |                                                           |                     |                                                                                                                                                                                                                                                                  |                   |

| Display       | EDT<br>ETM070001ADH6                                      |                     | 7" Capacitive touch screen. 800 x 480 pixels with white leds for the backlight. (Possibility to use a resistive touch screen in replacement of the capacitive one)                                                                                               | CPU               |

| HDMI Out      | •HDMI connector  •TI PanelBus  Transmitter                | J8<br>U6            | <ul> <li>Allow to connect an HD TV in parallel of<br/>the 7" LCD display</li> <li>Convert the RGB bus of the CPU into a DVI<br/>compliant interface.</li> </ul>                                                                                                  | CPU<br>(fig.3)    |

| Display       | LCD alpha-<br>numeric                                     | DS1                 | Provide 4x20 characters. Driven by the Spartan6.                                                                                                                                                                                                                 | FPGA<br>(fig.2)   |

| Memory        | •                                                         |                     |                                                                                                                                                                                                                                                                  | •                 |

| DDR sdram     | 256MB                                                     | Module<br>Variscite | Run @ 400MHz. Only accessible by the processor.                                                                                                                                                                                                                  | CPU               |

| Flash         | 256MB                                                     | Module<br>Variscite | Only accessible by the processor. Used to store the processor code and FPGA bitstreams.                                                                                                                                                                          | CPU               |

| SDCard        | Molex Secure<br>Digital connector                         | U10                 | Provide an alternate storage memory for the processor code (OS, File system). Accessible at the boot of the CPU.                                                                                                                                                 | CPU<br>(fig.3)    |

| DDR2 sdram    | Micron<br>16MBx16x8banks<br>MT47H128M16RT<br>-25E:C       | U14                 | Run @ 800MHz. Only accessible by Spartan6. Provide a fast and large external storage memory.                                                                                                                                                                     | FPGA<br>(fig.2)   |

| Communication | S                                                         |                     |                                                                                                                                                                                                                                                                  |                   |

| 1/0           | •3x double USB<br>Host type A<br>•SMSC USB2517<br>USB HUB | J50,51,52<br>U14    | <ul> <li>These connectors are linked to the High speed USB 2.0 controller of the CPU module through an on-board USB HUB from SMSC. This HUB offers 7 high-speed ports.</li> <li>They provide access to various peripherals (mouse, keyboard, webcam).</li> </ul> | CPU<br>(fig.3)    |

| Туре            | Components /<br>Interfaces | Board<br>Reference | Description                                                    | Board<br>Location |

|-----------------|----------------------------|--------------------|----------------------------------------------------------------|-------------------|

| 1/0             | 1x mini USB OTG            | J48                | Directly connected to the USB 2.0 OTG                          | CPU               |

|                 |                            |                    | controller of the CPU module.                                  | (fig.3)           |

| 1/0             | Ethernet 100Mb             | J13                | The Ethernet functionality is natively                         | CPU               |

|                 |                            |                    | supported by CPU module. Only the                              | (fig.3)           |

|                 |                            |                    | connector is located on the CPU board.                         |                   |

| Wifi /          | ·LS Research               | U20                | ·The Tiwi module is offering Wifi and                          | CPU               |

| Bluetooth       | Tiwi-R2 module             |                    | Bluetooth functionalities. It supports                         | (fig.3)           |

|                 |                            |                    | 802.11 b/g/n speed and BT 2.1. It is                           |                   |

|                 |                            |                    | directly connected to the CPU module.                          |                   |

|                 | ·SMA connector             | J14                | ·An SMA connector provides antenna                             |                   |

|                 |                            |                    | connection for both Wifi and Bluetooth                         |                   |

|                 |                            |                    | communications.                                                |                   |

| 3G / GPS        | ·Ericsson                  | J10                | This module provides access to 3.5G                            | FPGA              |

|                 | F5321GW                    |                    | protocols and to a GPS system. This is a                       | (fig.2)           |

|                 | module                     |                    | mini PCI Express form factor module. It is                     |                   |

|                 |                            |                    | connected to the HUB U14.                                      |                   |

|                 | ·SIM card con.             | P2                 | The SIM card is directly managed by the                        |                   |

|                 |                            |                    | Ericsson module itself.                                        |                   |

| High-speed      | Spartan6                   | P3 – P8            | Provides 3GHz links from Spartan6                              | FPGA              |

| links           | transceivers               |                    | transceivers through differential pairs                        | (fig.2)           |

|                 |                            |                    | connected to SMB connectors.                                   |                   |

| PCIe links      | Spartan6                   |                    | Provides two PCI Express lanes between                         | FPGA -            |

|                 | transceivers               |                    | the Spartan6 and the CPU board. PCI                            | CPU               |

|                 |                            |                    | reference clock is coming from an on-                          |                   |

|                 |                            |                    | board reference oscillator or could be                         |                   |

|                 |                            |                    | driven directly from the CPU board.                            |                   |

|                 |                            |                    | (This functionality is not available on the current CPU        |                   |

|                 |                            |                    | board.)                                                        |                   |

| SATA links      | Spartan6                   | J32                | Provides one SATA 1 connection between                         | FPGA -            |

|                 | transceivers               |                    | the Spartan6 and the CPU board.                                | CPU               |

|                 |                            |                    | (This functionality is not available on the current CPU board) | (fig.2)           |

|                 |                            |                    | In addition, a second link is available                        |                   |

|                 |                            |                    | through an external SATA connector (J32).                      |                   |

|                 |                            |                    | (This connection is third vendor IP dependent and not          |                   |

|                 |                            |                    | provided by the REDS.)                                         |                   |

| Expansion       | Samtec FMC LPC             | J6, J7             | Provides 34 differential lines or 58 single-                   | FPGA              |

|                 |                            |                    | ended signals per FMC connectors. They                         | (fig.2)           |

|                 |                            |                    | are linked directly to the Spartan6.                           |                   |

| Expansion       | DDK DHB 80 pin             | J5                 | Provides 78 GPIOs (2 GND). Mainly used to                      | FPGA              |

|                 |                            |                    | connect to REDS proprietary boards                             | (fig.2)           |

| General user in |                            |                    |                                                                | 1                 |

| User button     | Spartan3AN User            | SW13,              | Provides user dedicated buttons to the                         | FPGA              |

|                 | Button                     | SW14               | Spartan3AN.                                                    | (fig.4)           |

| Jumpers         | FTDI Jumper                | W11,               | Disconnect Eeprom from FTDI chip U8                            | FPGA <sup>4</sup> |

|                 | eeprom                     | W12, W13           | when removed.                                                  | (fig.4)           |

| Connector       | I2C connector              | W2                 | Provide access to the on-board I2C bus.                        | FPGA              |

|                 |                            |                    |                                                                | (fig.5)           |

$^4$  Only available on version 1.0 of the Reptar board

| Туре             | Components / Interfaces | Board<br>Reference | Description                               | Board<br>Location |

|------------------|-------------------------|--------------------|-------------------------------------------|-------------------|

| Connector        | SPI connector           | W3                 | Provide access to the on-board SPI bus.   | FPGA              |

| Connector        | 31 1 connector          | ***3               | Trovide decess to the off board 511 bas.  | (fig.5)           |

| Connector        | UART connector          | W6                 | Provide access to the on-board UART bus.  | FPGA              |

| Connector        | OAITI COMICCION         | ***                | Trovide decess to the off board OANT bas. | (fig.5)           |

| Connector        | CAN connection          | J45, U27           | Provide a compliant CAN bus connection    | FPGA              |

|                  |                         |                    | with the Spartan6.                        | (fig.2)           |

| Switch           | Spartan6 user           | S4                 | Provides a user dedicated 10 positions    | FPGA              |

|                  | switch                  |                    | switch to the Spartan6.                   | (fig.4)           |

| Buttons          | Spartan6 user           | SW1 to             | Provides 8x user dedicated buttons to the | FPGA <sup>5</sup> |

| 20.000.10        | Spartano asc.           | SW8                | Spartan6.                                 | (fig.4)           |

| Leds             | Spartan6 user leds      | D21 to             | Provides 8x user dedicated leds from the  | FPGA <sup>5</sup> |

| 2003             | Spartano aser reas      | D28                | Spartan6.                                 | (fig.4)           |

| Buttons          | CPU user buttons        | SW9 to             | Provides 4x user dedicated buttons to the | FPGA <sup>5</sup> |

| Dattons          | Ci o aser sattoris      | SW12               | CPU                                       | (fig.4)           |

| Leds             | CPU user leds           | D18 to             | Provides 3x user dedicated leds from the  | FPGA <sup>5</sup> |

| Leus             | Ci O user ieus          | D20                | CPU                                       | (fig.4)           |

| Buttons          | CPU user buttons        | SW0 to             | Provides 5x user dedicated buttons to the | CPU <sup>5</sup>  |

| buttons          | CFO user buttons        | SW4                | CPU                                       | (fig.7)           |

| Leds             | CPU user leds           | LED0 to 3          | Provides 3x user dedicated leds from the  | CPU <sup>5</sup>  |

| Leus             | CFO user leus           | LEDU to 3          | CPU                                       | (fig.7)           |

| Consous and Astr |                         | L                  | CPO                                       | 019.77            |

| Sensors and Act  |                         | 1120               | Duranida ta una anatama (ISC limb)        | FDCA              |

| Sensor           | Temperature             | U20                | Provide temperature (I2C link)            | FPGA<br>(fig.5)   |

| Sensor           | Light                   | U22                | Provide luminosity (I2C link)             | FPGA              |

| 3611301          | Ligiti                  | 022                | Frovide laminosity (IZC IIIIK)            | (fig.5)           |

| Sensor           | Accelerometer           | U21                | Provide accelerometer measure (SPI link)  | FPGA              |

| 2000.            | 7 1000101 01110101      |                    | Tremae accelerences measure (c. r)        | (fig.5)           |

| Button           | Incremental             | SW15               |                                           | FPGA              |

|                  | Encoder                 |                    |                                           | (fig.4)           |

| Buzzer           | TDK Magnetic            | U28                |                                           | FPGA              |

|                  | buzzer                  |                    |                                           | (fig.2)           |

| AD & DA          | <b>.</b>                |                    | 1                                         |                   |

| ADC              | Analog Device           | U25, J33,          | 12bit, 4 channels analog-to-digital       | FPGA              |

|                  | ADS7950                 | J34, J35,          | converter. It is connected to 4x two pins | (fig.5)           |

|                  |                         | J36                | screw terminals.                          |                   |

| DAC              | Analog Device           | U26, J41,          | 12bit, 4 channels digital-to-analog       | FPGA              |

| 57.10            | AD7398                  | J42, J43,          | converter. It is connected to 4x two pins | (fig.5)           |

|                  | 7.57550                 | J44                | screw terminals.                          |                   |

| Audio            |                         | 1 3                | Service Communication                     |                   |

| Digital          | Toshiba Toslink         | J31, J40           | Provide I/O optical audio links to the    | FPGA              |

| Digital          | TOSTIIDA TOSIIIK        | 131, 140           | Spartan6                                  | (fig.4)           |

| Analog Line IN   | 1x Jack connector       | J2                 | Audio IN link to the CPU.                 | CPU               |

| THE IN           | TV Jack COUNTECTOR      | 32                 | Addition in the to the CFU.               | (fig.3)           |

| Preamp. Line     | 1x Jack connector       | J3                 | Audio OUT from the CPU.                   | CPU               |

| OUT              |                         |                    |                                           | (fig.3)           |

|                  | 1x Jack connector       | J1                 | MIC Line to the CPU.                      | CPU               |

| MIC Line         |                         | 1 44               | I ITIIO EIIIC IO IIIC CI O.               |                   |

$^{5}$  Partially available on version 0.1 / Fully available on version 1.0  $\,$

janvier 2013 - 15 - REDS

| Туре             | Components /                                         | Board                           | Description                                                                                                                                                       | Board                        |

|------------------|------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                  | Interfaces                                           | Reference                       |                                                                                                                                                                   | Location                     |

| Clocking Circuit |                                                      |                                 | 1                                                                                                                                                                 |                              |

| 100MHz           | Main Spartan6 oscillator                             | Y3                              | Used to clock internal logic of the Spartan6. It is used to drive the FPGA internal PLLs.                                                                         | FPGA                         |

| 100MHz           | Main Spartan3AN oscillator                           | Y5                              | Used to clock internal logic of the Spartan3AN.                                                                                                                   | FPGA                         |

| 25MHz            | Common<br>oscillator to<br>Spartan6 and<br>Spartan3A | Y2                              | Optional slow clock for both FPGAs.                                                                                                                               | FPGA                         |

| 125MHz           | Dedicated PCIe<br>oscillator                         | U23                             | Provide standard clock for the dedicated transceiver PLL used for the PCI Express interface.                                                                      | FPGA                         |

| 150MHz           | Dedicated SATA oscillator                            | Y4                              | Provide standard clock for the dedicated transceiver PLL used for the SATA interface.                                                                             | FPGA                         |

| Configuration ci | rcuitry                                              |                                 |                                                                                                                                                                   |                              |

| Configuration    | Xilinx XCF32P<br>PlatformFlash                       | U36                             | Used to store up to 4 compressed bit-<br>streams for the Spartan6. Could be used in<br>Slave or Master modes.<br>Programmable through the main JTAG<br>chain.     | FPGA<br>(fig.2)              |

| Mode switch      | Spartan3AN<br>modes selector                         | S7                              | Bit 7 to 9 select the configuration mode of the Spartan3AN. Others are user dedicated.                                                                            | FPGA<br>(fig.4)              |

| Button           | Spartan6 Reset                                       | S9                              | Used to reset the Spartan6.                                                                                                                                       | FPGA<br>(fig.5)              |

| LED              | Spartan6<br>ConfDone                                 | D30                             | If on, the Spartan6 is not configured.                                                                                                                            | FPGA<br>(fig.5)              |

| Button           | Spartan3AN Reset                                     | S8                              | Used to reset the Spartan3AN bitstream.                                                                                                                           | FPGA<br>(fig.5)              |

| LED              | Spartan3AN<br>ConfDone                               | D49                             | If on, the Spartan3AN is not configured.                                                                                                                          | FPGA<br>(fig.5)              |

| Jumper           | Spartan6 CSI                                         | W17                             | Used to disconnect Chip Select functionality (for readback feature) when removed.                                                                                 | FPGA <sup>4</sup>            |

| Jumper           | Spartan6 RDWR                                        | W16                             | Used to disconnect readback functionality when removed.                                                                                                           | FPGA <sup>4</sup>            |

| Jumper           | Spartan6 VCCO_0 HSWAPEN                              | P1                              | Unable HSWAPEN functionality for Spartan6 when removed.                                                                                                           | FPGA<br>(fig.5)              |

| Jumpers          | JTAG chain<br>selector                               | W7, W8,<br>W9, W10,<br>W14, W15 | Taken by two, they allow bypassing FMC2 or FMC1 or PlatformFlash respectively, when in position 2-3.                                                              | FPGA <sup>4</sup><br>(fig.6) |

| JTAG Mux         | JTAG source<br>selection                             | U30, U32                        | Allow to choose between the JTAG 14 pins connector and the Digilent USB JTAG emulator as the source of the main JTAG chain. This mux is driven by the Spartan3AN. | FPGA<br>(fig.2)              |

| Туре         | Components /<br>Interfaces                                       | Board<br>Reference                 | Description                                                                 | Board<br>Location               |

|--------------|------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------|---------------------------------|

| Debug        |                                                                  |                                    |                                                                             |                                 |

| Headers      | 2x 16 pins headers                                               | J38, J39                           | Provides debug means for the Spartan6.                                      | FPGA<br>(fig.5)                 |

| Headers      | 1x 16 pins headers                                               | J8                                 | Provides debug means for the Spartan6.                                      | FPGA<br>(fig.5)                 |

| Headers      | 1x 8 pins headers                                                | W1                                 | Provides debug means for the Spartan6.                                      | FPGA<br>(fig.5)                 |

| Mictor       | 1x 38 pins Mictor                                                | J31                                | Provides debug means for the Spartan6.                                      | FPGA<br>(fig.2)                 |

| Mictor       | 1x 38 pins Mictor                                                | J48                                | Provides debug means for the Spartan3AN.                                    | FPGA<br>(fig.2)                 |

| Console      | ·1x CP2103 UART<br>to USB interface<br>·1x Mini-USB<br>connector | U11, J43                           | Linux console access via a Mini-USB connector.                              | CPU<br>(fig.7 & 3)              |

| JTAG         | 1x JTAG TI connector                                             | J29                                | Provides debug means for the CPU.                                           | CPU<br>(fig.3)                  |

| Headers      | 1x 8 pins header                                                 | W1                                 | Provides debug means for the CPU.                                           | CPU<br>(fig.7)                  |

| Power supply |                                                                  |                                    |                                                                             |                                 |

| LED          | Power LED                                                        | D51, D50,<br>D53, D54,<br>D52, D55 | When on, indicated good power state for 5V, 2V5, 3V3, 12V, 1V8 and DDR2_1V8 | FPGA <sup>4</sup><br>(on board) |

| Jumper       | Spartan6 VCCO_0 power selector                                   | W4                                 | Allow to power Spartan6 bank 0 from 2V5 or 3V3.                             | FPGA<br>(fig.6)                 |

| Jumper       | Spartan6 VCCO_3 power selector                                   | W5                                 | Allow to power Spartan6 bank 3 from 2V5 or 3V3.                             | FPGA <sup>4</sup> (fig.6)       |

| LED          | Power LED                                                        | D10, D12,<br>D13, D20              | When on, indicated good power state for 1V8, 3V3, 5V and 12V                | CPU<br>(on board)               |

| Jumper       | CPU VIO source selector                                          | W2                                 | Choose VIO 1V8 source from FPGA board or COM Module internal regulator      | CPU<br>(fig.7)                  |

| Power RTC    | CR1225                                                           | X1                                 | 3V battery for RTC                                                          | CPU                             |

Table 1 - Components & Functionalities details

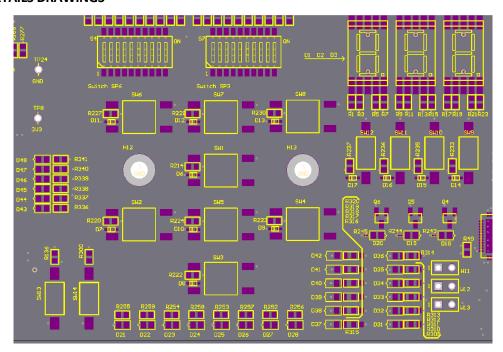

### 3.3 DETAILS DRAWINGS

Figure 4- FPGA General User Interfaces

Figure 5 – FPGA Config & Debug switches

Figure 6 - FPGA Jumpers

Figure 7 - CPU Label References

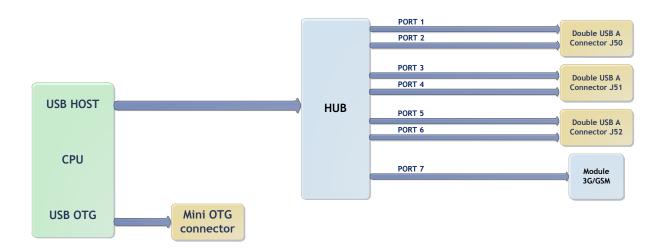

#### 3.4 USB INTERFACE

The USB sub-system of the REPTAR board is located onto the CPU board.

The CPU module from Variscite provides two USB 2.0 high-speed controllers. One is a HOST controller and the other is an OTG controller.

The OTG is directly linked to a mini OTG connector, whereas the HOST is attached to a USB HUB 7 ports.

- 6 ports are directly linked to double USB A connectors.

- The remaining port is used to connect, through the BTB<sup>6</sup> connectors, the 3G/GPS module located on the FPGA board.

Figure 8 - USB Sub-system

<sup>&</sup>lt;sup>6</sup> Board-To-Board connector used to link the CPU and the FPGA boards together.

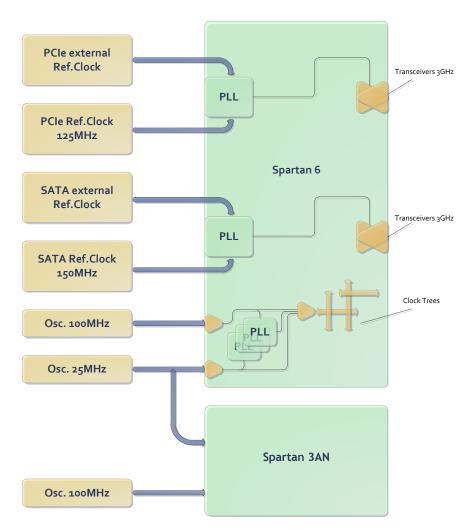

#### 3.5 CLOCKING CIRCUITRY

The REPTAR board's clocking circuitry is designed to be simple, reliable and easy to use.

Two separate 100MHz oscillators are used to drive the clocking trees of the Spartan6 and the Spartan3AN.

A slow oscillator at 25MHz is available for both FPGAs.

Separate oscillators provide stable references for the Spartan6 device's phase-locked loops (PLLs). These dedicated PLLs are used to distribute the PCI Express (125MHz), SATA (150MHz) clocks and DDR2 MCB blocs (not illustrated below).

Figure 9 - Spartan6 Clocks sub-system

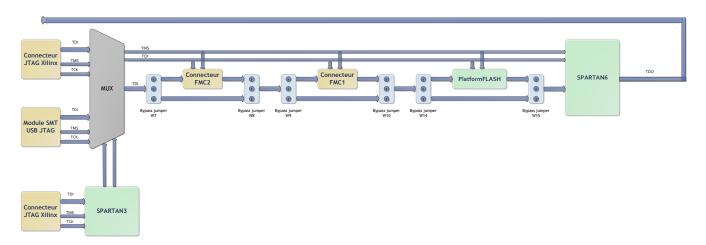

#### 3.6 JTAG CHAINS

### 3.6.1 FPGA

The configuration JTAG chain illustrated below is constituted of the following components:

- FMC2 connector

- FMC1 connector

- Xilinx PlatformFlash

- Xilinx Spartan6

This chain can be driven, through a discrete mux (controlled by the Spartan3AN), either by a standard 14-Pin connector or by a USB-JTAG module from Digilent (www.digilent.com).

The Digilent module allows connecting the REPTAR board directly to the Xilinx Impact programming tool using a simple USB cable.

It is also possible to use a standard Xilinx USB Platform Cable connected to the 14-Pin connector.

Figure 10 - JTAG Chain

A second JTAG chain exists to program the Spartan3AN, only.

### 3.6.2 CPU

The JTAG chain for the CPU is mainly used to perform debugging with specific tools, such as Code Composer Studio. The JTAG connector onto the CPU board is compliant with TI emulators.

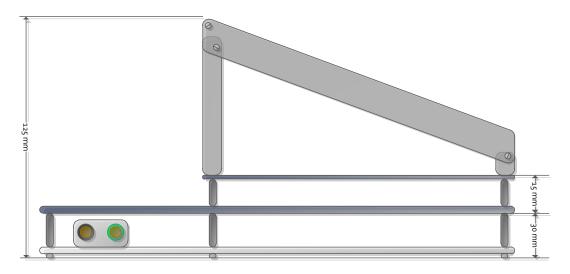

# 4. **DIMENSIONS**

Figure 11 - FPGA Board dimensions

Figure 12 - CPU Board dimensions

This side view shows from bottom to top:

- Plexiglas Support

- FPGA mainboard

- CPU board

- 7" display (at 30°)

Figure 13 - REPTAR Board side view

### 5. POWER SUPPLIES

The main circuitry is a Linear Technologies  $\mu$ Module LT4628. It supports an <u>input voltage</u> <u>between 7V and 26V</u> and generates a main <u>5V/16A output</u> for the other regulators.

Altogether, including two FMC boards connected to the board, <u>REPTAR will consume around 80 Watt</u>.

The image below shows the power supplies of the REPTAR board and the main peripherals powered by them.

### 6. ADDITIONAL INFORMATION

### **6.1** REVISION HISTORY

| Chapter | Date      | Version | Changes Made                                        |

|---------|-----------|---------|-----------------------------------------------------|

| All     | June 2012 | 1.0     | <ul><li>First publication /Proto1 (v0.1)</li></ul>  |

| All     | Sept 2012 | 1.1     | <ul> <li>Modifications for Proto2 (v1.0)</li> </ul> |

Table 2 - Revision History

### 6.2 CONTACT

For the most up-to-date information about the REPTAR board, refer to the REDS wiki at wikireds.heig-vd.ch

Or, contact the REDS institute directly:

HEIG-VD REDS Institute Route de Cheseaux 1 CH-1401 Yverdon-les-Bains

reds@heig-vd.ch